# RZZ

# SYSTEM 4000

# FOR TUNER, HF VEHICLE ANTENNA PV 4330

# **TECHNICAL DESCRIPTION**

Issue: JUNE 1990

# AMENDMENT RECORD

| Amendment No. | Actioned by: Signature | Date |

|---------------|------------------------|------|

|               |                        |      |

|               |                        |      |

|               |                        |      |

|               |                        |      |

|               |                        |      |

| XII           |                        |      |

# TUNER, HF, VEHICLE ANTENNA (HF ATU)

# TECHNICAL DESCRIPTION

# INDEX OF TEXT

| Text                                              | V) |       | Para      |

|---------------------------------------------------|----|-------|-----------|

| INTRODUCTION                                      |    |       |           |

| GENERAL                                           |    |       | 1 - 4     |

| ARRANGEMENT OF EQUIPMENT                          |    |       |           |

| LAYOUT OF CONTROLS AND CONNECTORS                 |    |       | 5         |

| LAYOUT OF EQUIPMENT                               |    |       | 6-9       |

|                                                   |    |       |           |

| PRINCIPLES OF OPERATION                           |    |       | 22        |

| GENERAL                                           | 60 |       | 10        |

| Module 1 - Multiway Filter Board                  |    | 20 20 | 11        |

| Module 2 - Power Supply Unit                      |    |       | 12        |

| Module 3 - Microprocessor Board                   |    |       | 13 - 14   |

| Module 4 - Detector Module                        |    |       | 15        |

| Module 5 - RF Matching Board                      |    | 2     | 16        |

| Module 6 - RF Matching Board                      |    |       | 17        |

| FUNCTIONAL DESCRIPTION                            |    |       | 18 - 19   |

| Tuning Sequence                                   |    |       | 20 - 26   |

| 2FS                                               |    |       | 27 - 28   |

| Protection Circuits                               |    |       | 29        |

| MICROPROCESSOR PROGRAM CONTROL                    |    |       | 30 - 36   |

| DETAILED TECHNICAL DESCRIPTION                    |    |       |           |

| GENERAL                                           |    |       | 37 - 40   |

| RESET from HF R/T                                 |    |       | 41 - 45   |

| Transmit Following RESET                          |    |       | 46 - 48   |

| RF Power and Antenna DC Resistance Measurement    |    |       | 49 - 51   |

| Initial Component Selection                       |    |       | 52 - 55   |

| Tuning Sequence                                   |    |       | 56 - 64   |

| ATU Protection Signals                            |    |       | 65 - 67   |

| Temperature.                                      |    |       | 68        |

| Current.                                          |    |       | 69 -      |

| VSWR.                                             |    |       | 70 - 71   |

|                                                   |    |       | 72        |

| System Supply.<br>2FS                             |    |       | 73 - 76   |

| WEST Comments                                     |    |       |           |

| Power Supplies                                    |    |       | 77 - 80   |

| BITE                                              |    |       | 81 - 82   |

| MODULE 1 - MULTIWAY FILTER BOARD                  |    |       | 83        |

| General                                           |    |       | 83        |

| Circuit Description                               |    |       | 84 - 85   |

| MODULE 2 - POWER SUPPLY UNIT                      |    |       |           |

| General                                           |    |       | 86-88     |

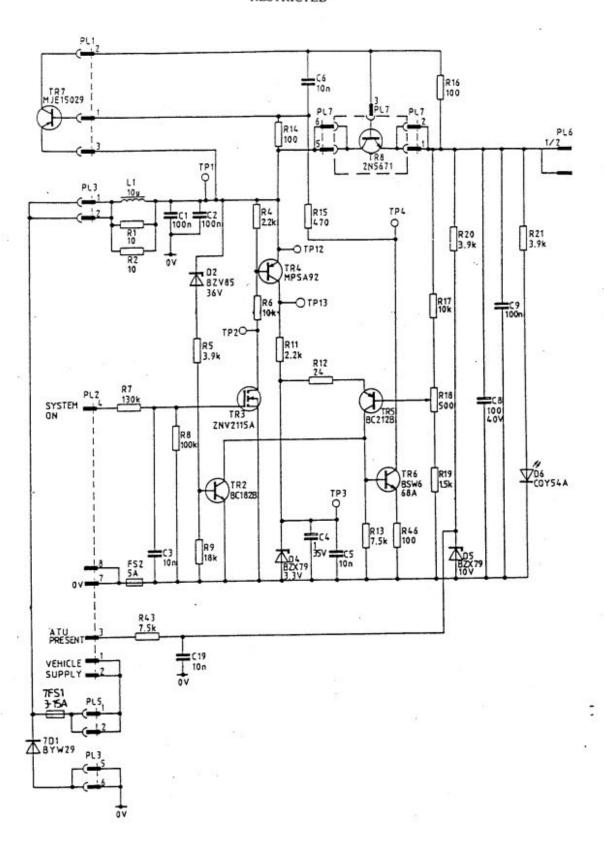

| Power Supply Control and +19 V Regulator Circuits |    |       |           |

| Power Supply Control.                             |    |       | 89 - 92   |

| +19 V Regulator Circuit.                          |    |       | 93 - 99   |

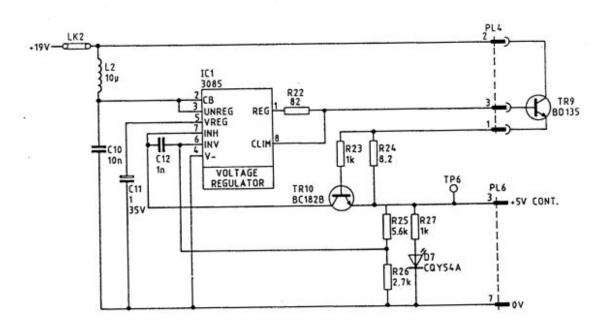

| +5 V Regulator Circuit.                           |    |       | 100 - 104 |

|                                                   |    |       | 105       |

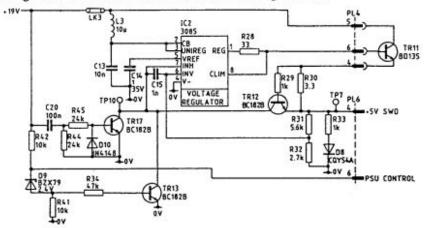

| +5 V (SWD) Regulator Circuit.                     |    |       | 106 - 108 |

| Delay Circuit.                                    |    |       |           |

| Switching Circuit.                                |    |       | 109 - 110 |

| +10 V (SWD) Regulator Circuit.                    |    |       | 10101     |

| MODULE 3 - MICROPROCESSOR BOARD                           |    |                |     |

|-----------------------------------------------------------|----|----------------|-----|

| General                                                   |    | 112 -          | 114 |

| Module 3 Inputs.                                          |    | 115            | 114 |

| Module 3 Outputs.                                         |    | 116            |     |

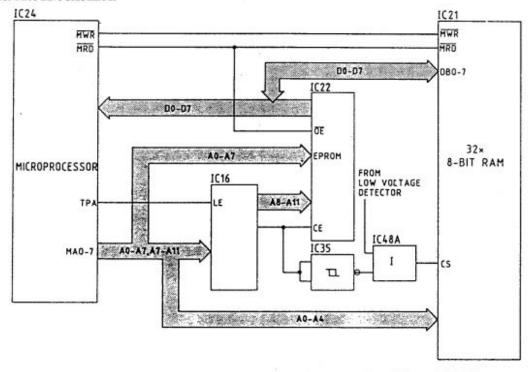

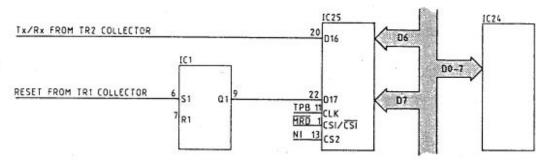

| Microprocessor and Program Memory Circuits                |    | 117 -          | 121 |

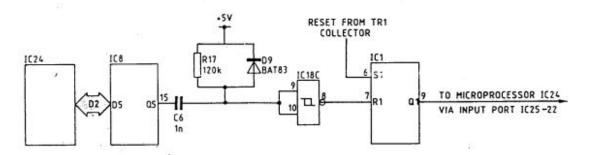

| Power-up Reset Circuit                                    |    | 112 -          |     |

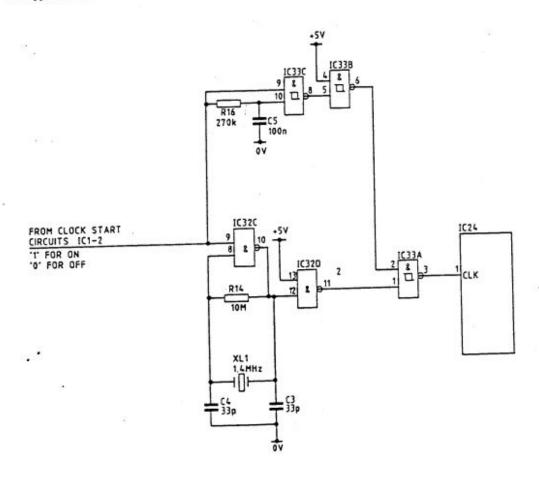

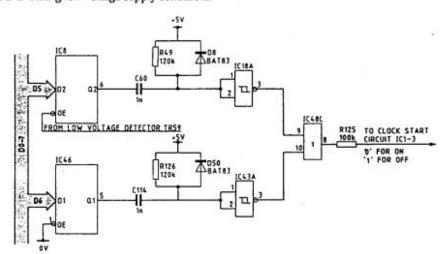

| Clock Circuit                                             | 46 | 128 -          |     |

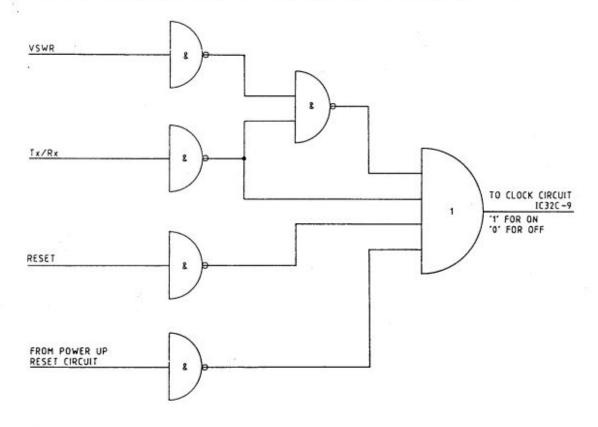

| Clock Start Circuit                                       |    | 133 -          |     |

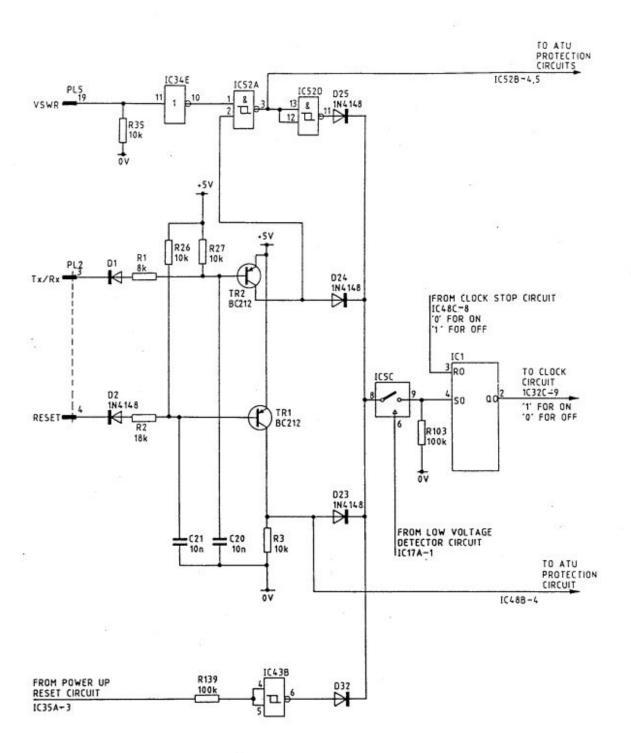

| Tx/Rx and RESET.                                          |    | 141 -          |     |

| VSWR.                                                     |    | 143 -          |     |

| Power-up Clock Start.                                     |    | 145            |     |

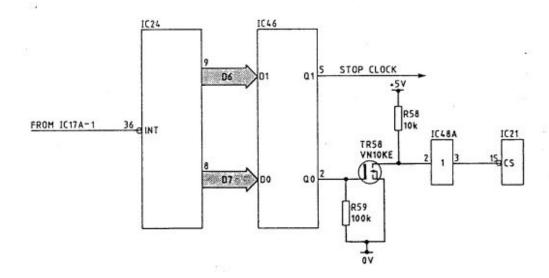

| Clock Stop Circuit                                        |    | 146 -          | 151 |

| RESET and Tx/Rx Input Circuits                            |    | 152 -          |     |

| Clear Reset Circuit                                       |    | 156 -          |     |

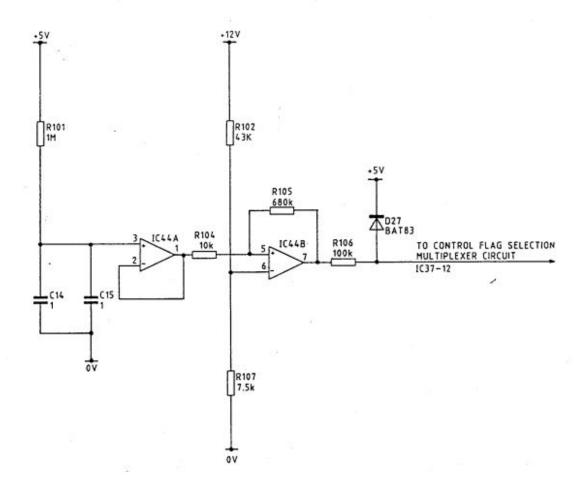

| Control Flag Selection Multiplexer Circuit                |    | 158 -          |     |

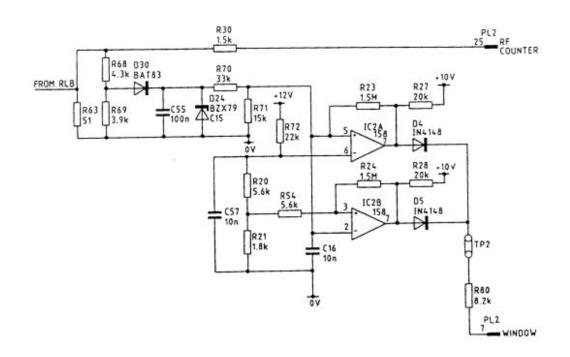

| Frequency Counter Circuit                                 |    | 165 -          |     |

| Analogue to Digital Converter Circuits                    | 19 | 173 -          |     |

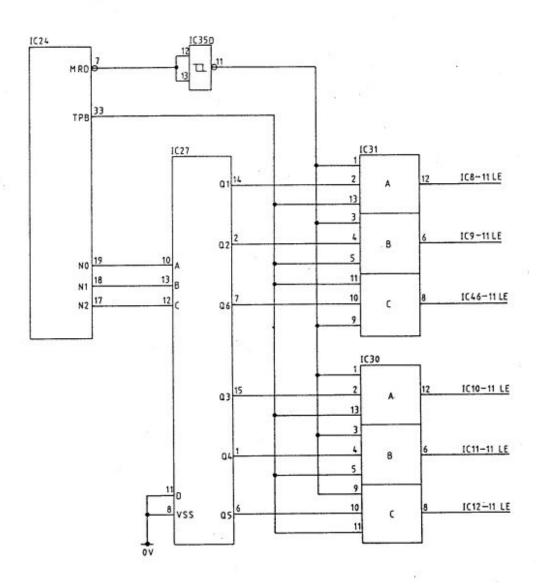

| D-Type Latches                                            |    | 186 -          |     |

| Output D-Type Latch Decoder Circuit.  Output Port Signals |    | 188 -          |     |

| Input Port Signals                                        | 7  | 193 -          | 194 |

| D-Type Latch Output Driver Circuits                       |    | 195            |     |

| System Control Signal Driver Circuit.                     |    | 196            | 100 |

| High Current Driver Circuits.                             |    | 197 -<br>200 - |     |

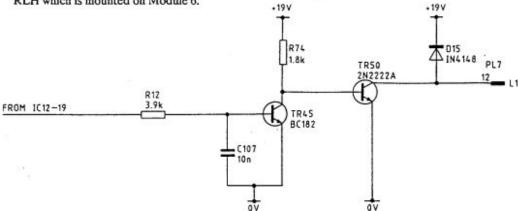

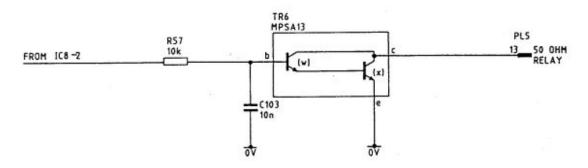

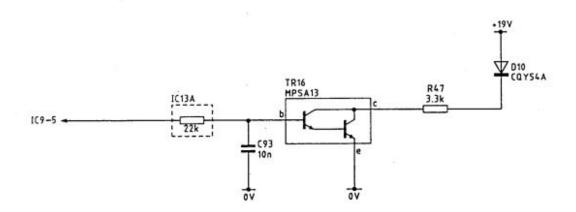

| Darlington Pair Drive Circuit.                            |    | 202 -          |     |

| Low Voltage Detector Circuit                              |    | 205 -          |     |

| D-Type Output Enable (OE).                                |    | 208            | 201 |

| 8-Bit Ram Chip Disable and Clock Stop Circuit.            |    | 209            |     |

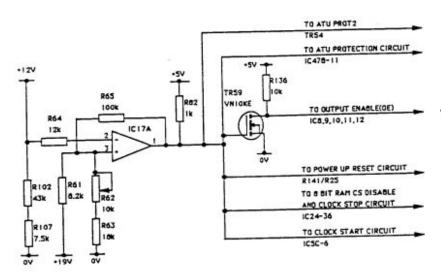

| Starting Disturbance Detector                             |    | 210 -          | 212 |

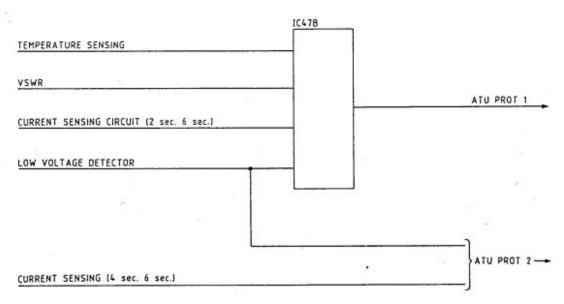

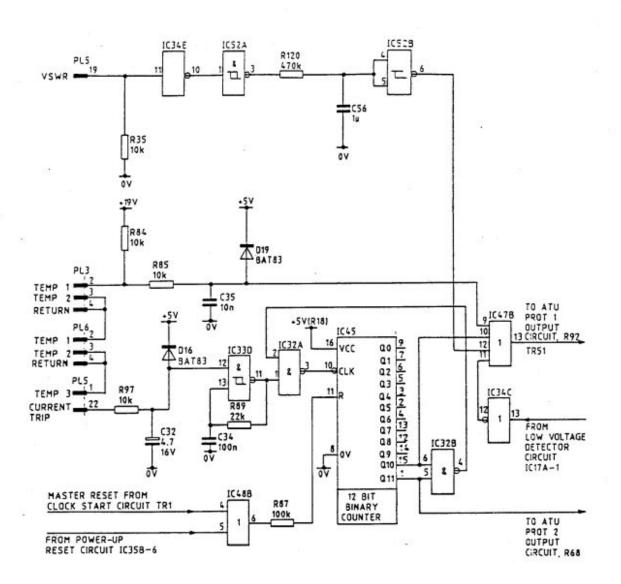

| ATU Protection Circuits                                   |    | 213 -          |     |

| Temperature Sensing Input Circuit.                        |    | 215 -          |     |

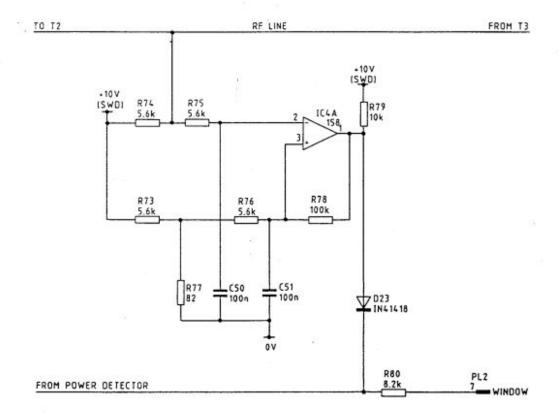

| VSWR Input Circuit.                                       |    | 217            |     |

| Low Volts Detector Input Circuit.                         |    | 218            |     |

| Current Sensing Circuit.                                  |    | 219 -          | 226 |

| ATU PROT 1/ATU PROT 2 Output Circuits                     |    |                |     |

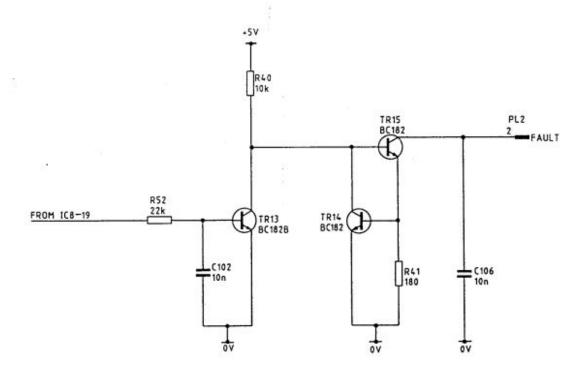

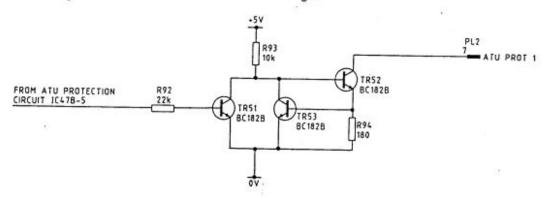

| ATU PROT 1.                                               |    | 227 -          |     |

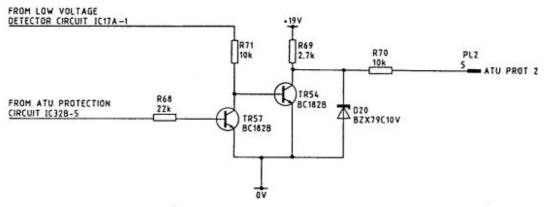

| ATU PROT 2.                                               |    | 229 -          |     |

| Voltage Supply Protection Circuits                        |    | 231 -          |     |

| PSU Control Switching<br>BITE RAM/ROM Tests               |    | 235 -          |     |

| RAM Test.                                                 |    | 237 -          | 238 |

| ROM Test.                                                 |    | 239            |     |

| HOW Test.                                                 |    | 240            |     |

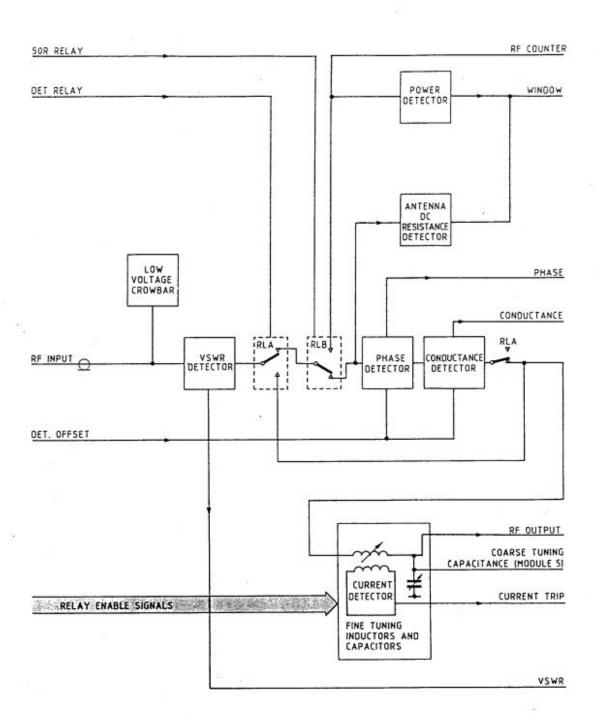

| MODULE 4 - DETECTOR MODULE                                |    |                |     |

| General                                                   |    | 241 -          | 246 |

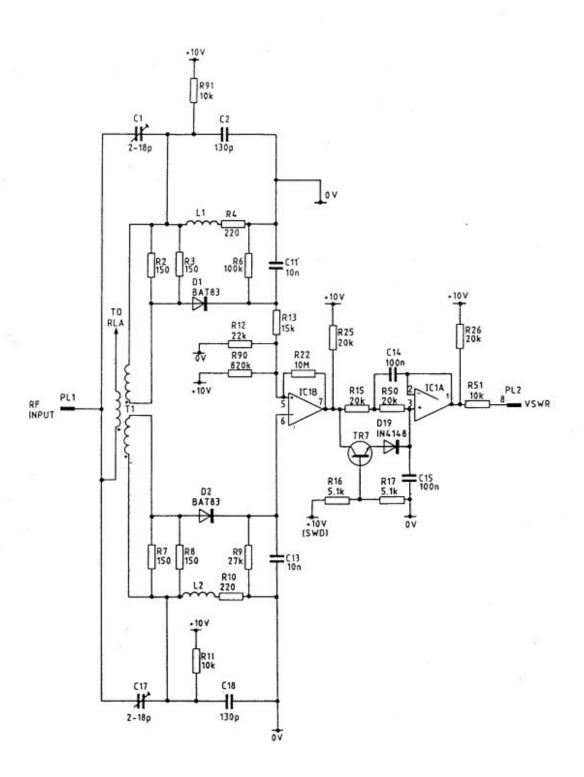

| VSWR Detector                                             |    | 247 -          |     |

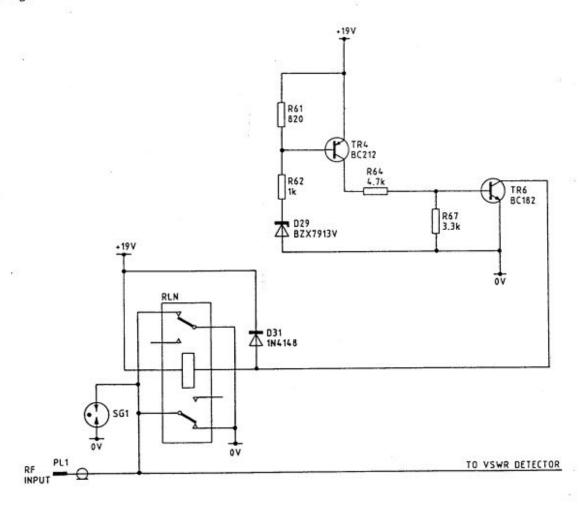

| Low Voltage Crowbar                                       |    | 254 -          |     |

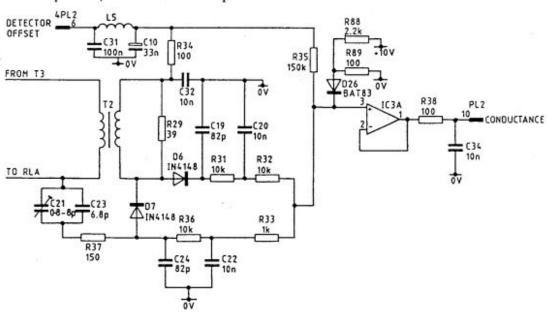

| Conductance Detector                                      |    | 258 -          |     |

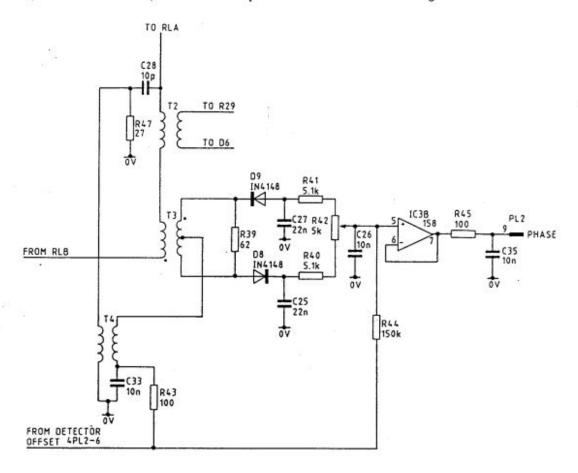

| Phase Detector                                            |    | 264 - :        |     |

| Power Detector                                            |    | 268 -          |     |

| Antenna DC Resistance Detector                            |    | 274 -          |     |

| Circulating Current Detector                              |    | 277 -          |     |

| Fine Tuning Inductor and Capacitor Selection              |    | 280 -          |     |

| Large Current Relays.                                     |    | 283 -          |     |

| Small Current Relays.                                     |    | 286 - 1        |     |

| Module Voltage Supplies                                   |    | 289 - 3        |     |

| HORNIES BEILIERUNG STEEL                                  |    |                |     |

| MODULE 5 - RF MATCHING BOARD                              |    |                |     |

| General                                                   |    | 292 - 1        |     |

| Circuit Description                                       |    | 295 - 2        | 298 |

| MODULE 6 - RF MATCHING BOARD               |           |

|--------------------------------------------|-----------|

| General                                    | 299 - 301 |

| Relay Circuitry.                           | 302 - 303 |

| Relay/Coarse Inductor Selection.           | 304 - 305 |

| Relay/Broadband Shunt Capacitor Selection. | 306 - 307 |

# INDEX OF FIGURES

| Elaura                           | index of Tradited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | Dom  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|

| Figure<br>FIGURE 1-              | TIMES HE VEHICLE ANTENNA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | Page |

| FIGURE 1-                        | TUNER, HF, VEHICLE ANTENNA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | 5    |

| FIGURE 2-                        | TUNER, HF, VEHICLE ANTENNA HF ATU FRONT PANEL HF ATU EQUIPMENT BLOCK DIAGRAM HF ATU FUNCTIONAL BLOCK DIAGRAM MICROPROCESSOR SYSTEM BASIC BLOCK DIAGRAM MICROPROCESSOR MEMORY STRUCTURE POWER SUPPLY INTERCONNECTION DIAGRAM TYPICAL LOW-PASS FILTER MODULE 2 FUNCTIONAL BLOCK DIAGRAM POWER SUPPLY CONTROL AND +19 V REGULATOR CIRCUITS +5 V REGULATOR CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                        |     | 6    |

| FIGURE 3-                        | HE ATH EUNICTIONAL DLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 11   |

| FIGURE 4-                        | MICROPROCESSOR SYSTEM BASIC BLOCK DIACRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 11   |

| FIGURE 5-                        | MICROPHOCESSOR STSTEM BASIC BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 100 | 13   |

| FIGURE 6-                        | MICHOPHOCESSOR MEMORY STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | 14   |

| FIGURE 7-                        | TYPICAL LOW PAGE SILTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 23   |

| FIGURE 8-                        | TYPICAL LOW-PASS FILTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 24   |

| FIGURE 9-                        | MODULE 2 FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 25   |

| FIGURE 10-                       | FOWER SUPPLY CONTROL AND +19 V REGULATOR CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 27   |

|                                  | TO THEODERICH ON CONT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |      |

|                                  | +5 V SWITCHED REGULATOR CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 29   |

| FIGURE 13-                       | MODULE 3 FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 31   |

| FIGURE 14-                       | MICROPROCESSOR AND MEMORY BASIC BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (5) | 34   |

|                                  | POWER-UP RESET CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 35   |

|                                  | CLOCK CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 36   |

|                                  | CLOCK START LOGIC DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 37   |

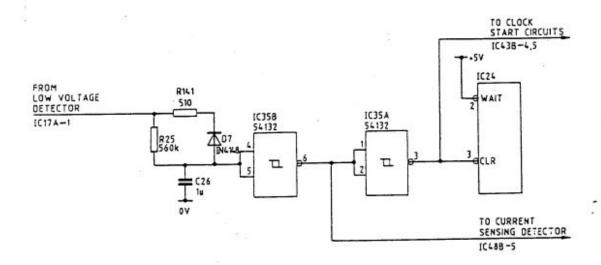

|                                  | CLOCK START CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 39   |

|                                  | CLOCK STOP CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | 40   |

|                                  | MODULE 3 FUNCTIONAL BLOCK DIAGRAM MICROPROCESSOR AND MEMORY BASIC BLOCK DIAGRAM POWER-UP RESET CIRCUIT CLOCK CIRCUIT CLOCK START LOGIC DIAGRAM CLOCK START CIRCUIT CLOCK STOP CIRCUIT RESET AND TX/RX INPUT CIRCUITS CLEAR RESET CIRCUIT MULTIPLEXER FUNCTIONAL DIAGRAM CONTROL AND MULTIPLEXER CIRCUIT FREQUENCY COUNTER CIRCUIT ANALOGUE TO DIGITAL CONVERTER CIRCUIT OUTPUT D-TYPE LATCH DECODER CIRCUIT SYSTEM CONTROL SIGNAL DRIVER CIRCUIT HIGH CURRENT DRIVER CIRCUITS DARLINGTON PAIR DRIVE CIRCUIT 8-BIT RAM DISABLE AND CLOCK STOP CIRCUIT STARTING DISTURBANCE DETECTOR CIRCUIT ATU PROT 1/ATU PROT 2 LOGIC DIAGRAM ATU PROTECTION CIRCUITS ATU PROT 1 OUTPUT CIRCUIT LOD DIO DRIVER CIRCUIT LED DIO DRIVER CIRCUIT LED DIO DRIVER CIRCUIT |     | 41   |

|                                  | CLEAR RESET CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 41   |

|                                  | MULTIPLEXER FUNCTIONAL DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 42   |

|                                  | CONTROL AND MULTIPLEXER CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | 43   |

|                                  | FREQUENCY COUNTER CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 45   |

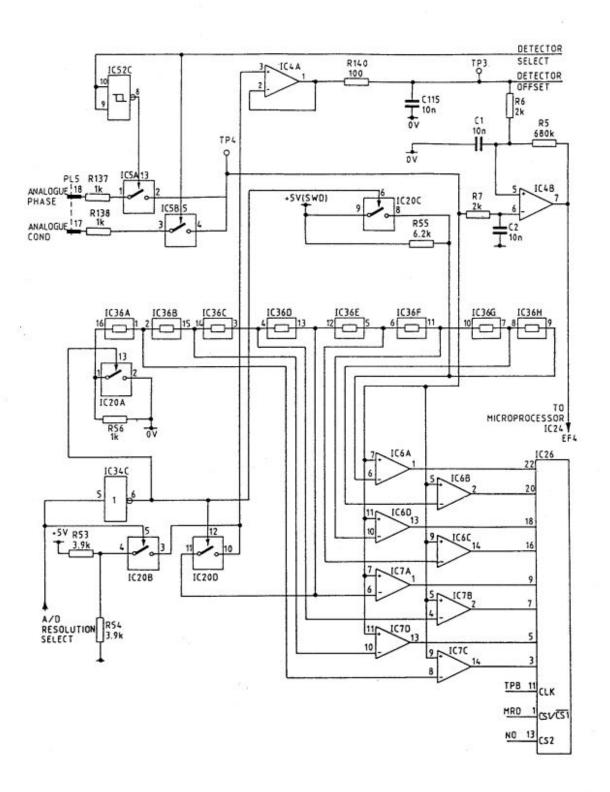

|                                  | ANALOGUE TO DIGITAL CONVERTER CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 47   |

|                                  | OUTPUT D-TYPE LATCH DECODER CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 51   |

| Converse State and Conference of | SYSTEM CONTROL SIGNAL DRIVER CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 54   |

|                                  | HIGH CURRENT DRIVER CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 55   |

|                                  | DARLINGTON PAIR DRIVE CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 55   |

|                                  | LOW VOLTAGE DETECTOR CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 56   |

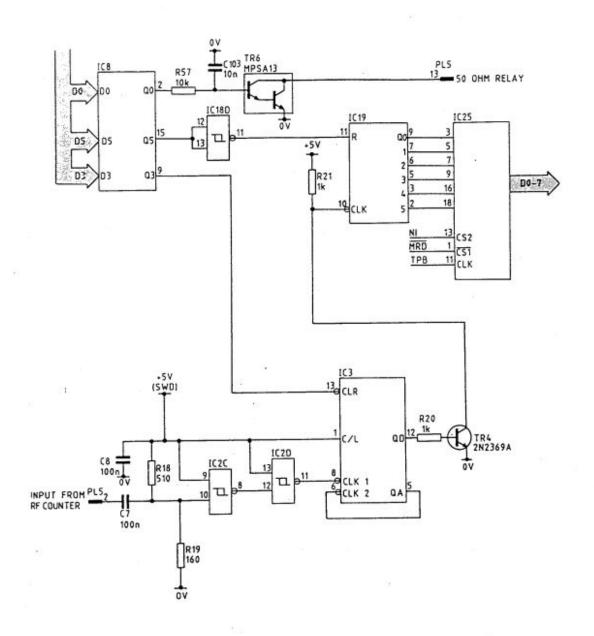

| FIGURE 31-                       | 8-BIT RAM DISABLE AND CLOCK STOP CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 57   |

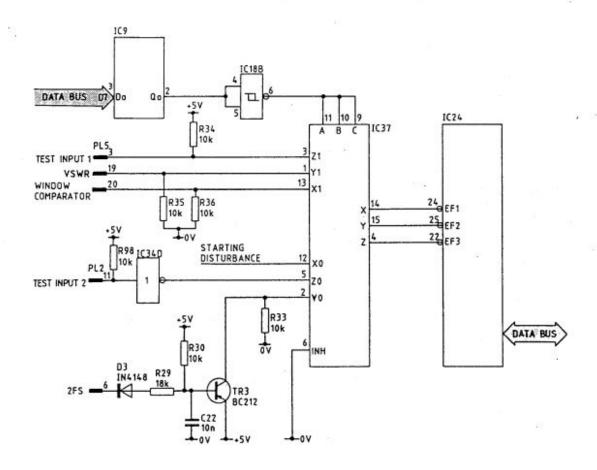

| FIGURE 32-                       | STARTING DISTURBANCE DETECTOR CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 58   |

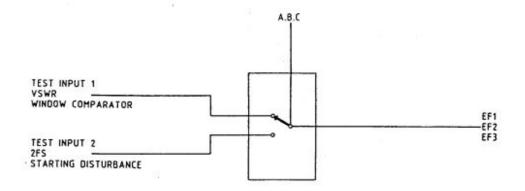

| FIGURE 33-                       | ATU PROT 1/ATU PROT 2 LOGIC DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 59   |

| FIGURE 34-                       | ATU PROTECTION CIRCUITS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 61   |

| FIGURE 35-                       | ATU PROT 1 OUTPUT CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 62   |

| FIGURE 36-                       | ATU PROT 2 OUTPUT CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 62   |

| FIGURE 37-                       | LED DIO DRIVER CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 64   |

| FIGURE 38-                       | MODULE 4 FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 67   |

| FIGURE 39-                       | VSWR CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 69   |

| FIGURE 40-                       | LOW VOLTAGE CROWBAR CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 70   |

| FIGURE 41-                       | CONDUCTANCE DETECTOR CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 71   |

| FIGURE 42-                       | PHASE DETECTOR CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 72   |

| FIGURE 43-                       | POWER DETECTOR CIRCUIT DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 73   |

| FIGURE 44-                       | ANTENNA DC RESISTANCE DETECTOR CIRCUIT DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 74   |

| FIGURE 45-                       | STARTING DISTURBANCE DETECTOR CIRCUIT ATU PROT 1/ATU PROT 2 LOGIC DIAGRAM ATU PROTECTION CIRCUITS ATU PROT 1 OUTPUT CIRCUIT ATU PROT 2 OUTPUT CIRCUIT LED DIO DRIVER CIRCUIT MODULE 4 FUNCTIONAL BLOCK DIAGRAM VSWR CIRCUIT LOW VOLTAGE CROWBAR CIRCUIT CONDUCTANCE DETECTOR CIRCUIT PHASE DETECTOR CIRCUIT POWER DETECTOR CIRCUIT DIAGRAM ANTENNA DC RESISTANCE DETECTOR CIRCUIT LARGE CURRENT DETECTOR CIRCUIT SMALL CURRENT RELAY DRIVE CIRCUIT MODULE 5 FUNCTIONAL BLOCK DIAGRAM MODULE 6 FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                |     | 75   |

| FIGURE 46-                       | LARGE CURRENT RELAY DRIVE CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 76   |

| FIGURE 47-                       | SMALL CURRENT RELAY DRIVE CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 77   |

| FIGURE 48-                       | MODULE 5 FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 79   |

| FIGURE 40                        | MODULE 6 FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 81   |

| 1 100116 43                      | MODULE OF ONO HOMAE DECOM DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 01   |

RESTRICTED

| FIGURE 1001-<br>FIGURE 1002-<br>FIGURE 1003-<br>FIGURE 1004-<br>FIGURE 1005-<br>FIGURE 1006-<br>FIGURE 1007- | MODULE 3 CIRCUIT DIAGRAM<br>MODULE 4 CIRCUIT DIAGRAM<br>MODULE 5 CIRCUIT DIAGRAM<br>MODULE 6 CIRCUIT DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1001/1002<br>1003/1004<br>1005/1006<br>1007/1008 - 1011/1012<br>1013/1014 - 1015/1016<br>1017/1018<br>1019/1020 |

|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| FIGURE 1007-<br>FIGURE 1008-                                                                                 | THE THE PARTY OF T | 1021/1022                                                                                                       |

# INDEX OF TABLES

| Table             |                                                       | rage    |

|-------------------|-------------------------------------------------------|---------|

| TABLE 1-          | FUNCTION OF CONNECTORS AND CHART                      | 6       |

| TABLE 2-          | HF ATU FRONT PANEL CONTROL INPUTS                     | 15      |

| TABLE 3-          | HF ATU FRONT PANEL CONTROL OUTPUTS                    | 15      |

| TABLE 4-          | INITIAL COMPONENT SELECTION                           | 18      |

| TABLE 5-          | EFFECTS OF ENABLING ATU PROT 1 AND ATU PROT 2         | 20      |

| TABLE 6-          | MODULE 3 INPUT FUNCTIONS                              | 32      |

|                   | MODULE 3 OUTPUT FUNCTIONS                             | 33      |

| TABLE 7-          | MULTIPLEXER FLAG INPUTS                               | 42      |

| TABLE 8-          | EXAMPLE OF COMPARATOR COARSE DETERMINATION            | 46      |

| TABLE 9-          |                                                       | 48      |

| TABLE 10-         |                                                       | 49      |

| TABLE 11-         |                                                       | 50      |

| TABLE 12-         | BCD TO DECIMAL TRUTH TABLE                            | 52      |

| TABLE 13-         |                                                       | 53      |

| TABLE 14-         | INPUT PORT PIN FUNCTIONS                              | 64      |

| TABLE 15-         | BITE RAM/ROM TEST PASS INDICATION                     | 77      |

| TABLE 16-         | RELAY/COMPONENT SELECTION TABLE                       |         |

| TABLE 17-         | RELAY SWITCHING COMBINATIONS FOR RLF, RLG AND RLH     | 82      |

| <b>TABLE 1001</b> | - COMPONENT SCHEDULE - MULTIWAY FILTER BOARD MODULE 1 | 83      |

| TABLE 1002        | COMPONENT SCHEDULE - POWER SUPPLY UNIT MODULE 2       | 84 - 85 |

| TABLE 1003        | L COMPONENT SCHEDULE - MICROPROCESSOR BOARD MODULE 3  | 86 - 89 |

| TAR! F 1004       | L COMPONENT SCHEDULE - DETECTOR MODULE MODULE 4       | 90 - 92 |

| TABLE 1005        | COMPONENT SCHEDULE - RF MATCHING BOARD MODULE 5       | 93      |

| TABLE 1006        |                                                       | 94      |

# INTRODUCTION

# GENERAL

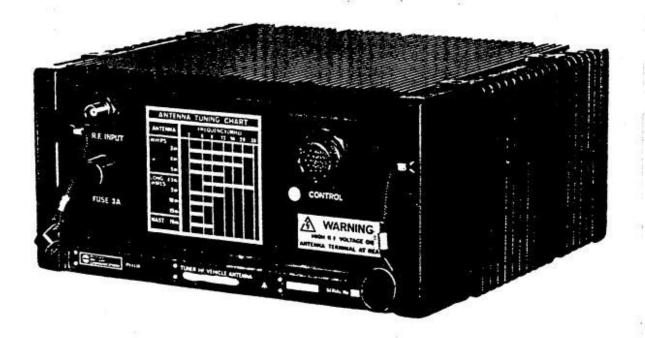

- The Tuner, HF, Vehicle Antenna (HF ATU) shown at Figure 1, is a Microprocessor-controlled Antenna Tuning Unit for use in ground or vehicle-borne HF transceiver stations.

- The HF ATU may be connected into the HF sub-system as follows:

- Between the vehicle antenna and the Amplifier, Radio Frequency, HF, 100W (HF PA).

- Between the vehicle antenna and the Filter, Bandpass, HF Cositing (CSF), if the HF PA is not fitted.

- c. Directly between the Receiver Transmitter, HF, HF PA nor HF CSF is fitted. (HF R/T) and the vehicle antenna if neither the

- 3. Operation of the HF ATU is fully automatic over its operating range of 2 to 30 MHz. The RF input power to the HF ATU is automatically reduced if the vehicle power supplies go low, and also if the HF ATU overheats or an unacceptable antenna mismatch occurs. The HF ATU operates from an unconditioned nominal 28 Vdc vehicle supply which is provide either directly by the HF R/T or, depending upon configuration, via the HF CSF or the HF PA.

- The HF ATU is of modular construction and consists of six panel electronic circuits plus a number of

chassis-mounted components. Provision for vehicle mounting is made via threaded holes located on flanges at the

side of the HF ATU.

FIGURE 1 - TUNER, HF, VEHICLE ANTENNA

# ARRANGEMENT OF EQUIPMENT

# LAYOUT OF CONTROLS AND CONNECTORS

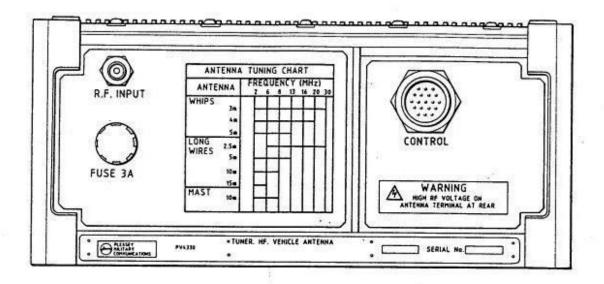

5. The layout of the HF ATU front panel is shown at Figure 2. Table 1 lists the functions of all connectors and charts. There are no manual controls.

FIGURE 2 - HF ATU FRONT PANEL

TABLE 1 - FUNCTION OF CONNECTORS AND CHART

| CONNECTOR OR CHART       | FUNCTION                                                |

|--------------------------|---------------------------------------------------------|

| R.F. INPUT               | RF input power from HF R/T, HF CSF or HF PA.            |

| CONTROL                  | Power and control lines to/from HF R/T, HF CSF or HF PA |

| ANTENNA TUNING CHART     | Combinations of antennae and operating frequencies.     |

| Screw terminal (at rear) | RF output to antenna.                                   |

# LAYOUT OF EQUIPMENT

- 6. The HF ATU is constructed as a single four-side aluminium casting with a ribbed bulkhead, and has detachable top and bottom covers with panclimatic seals. The electrical components are mounted on threaded bosses and the equipment is kept dry internally by a desiccator capsule which is mounted on the rear panel.

- 7. The case contains six panel electronic circuits/assemblies, five being mounted in the upper and lower compartments, and one mounted on the chassis. Five power transistors in the lower compartment are mounted on the chassis via thermally transparent insulating washers.

- 8. The front of the casting is fitted with the R.F. INPUT and CONTROL connectors and a fuse; the rear of the casting carries the antenna connector with associated insulator, the desiccator, and an earth stud. All front panel designations are clearly marked on a blackened aluminium plate. Internal connections of removable items are made via plug/socket type connectors.

- Two threaded holes (ISO Metric Coarse) on the flanges of the upper and lower surfaces of the case are available for attaching the HF PA to other HF equipments. All tapped holes are fitted with wire thread inserts.

# PRINCIPLES OF OPERATION

### GENERAL

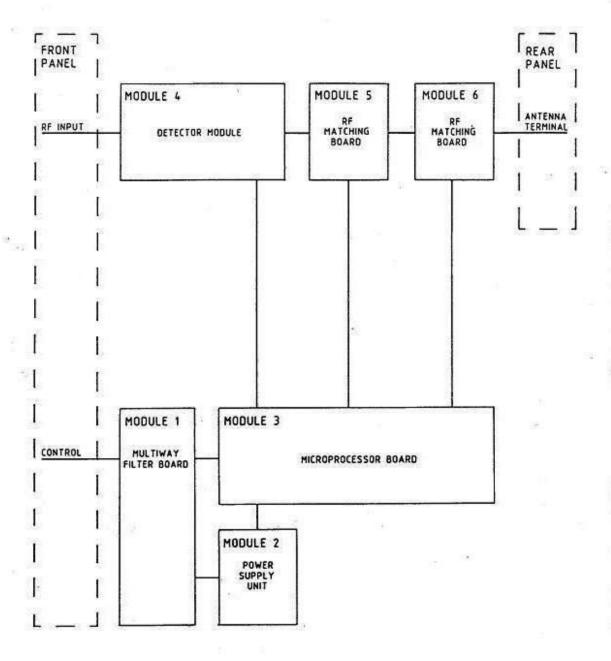

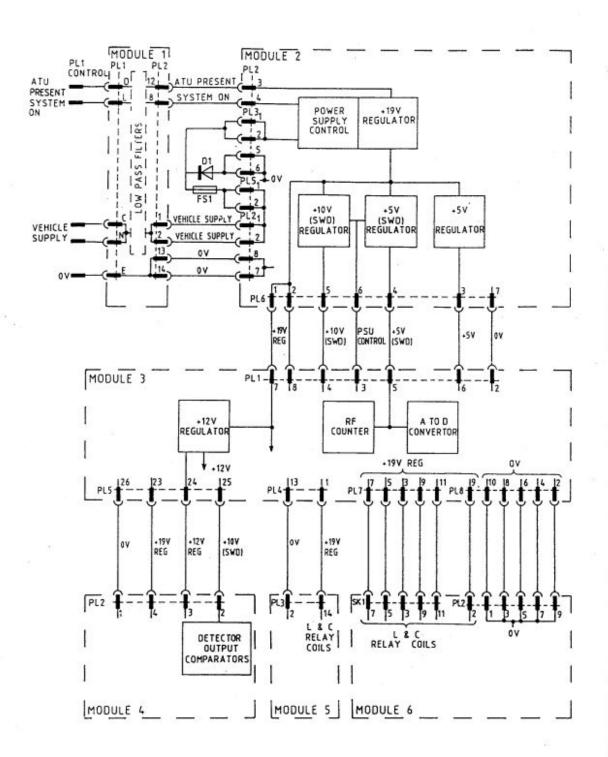

- 10. As shown in the equipment block diagram at Figure 3, the HF ATU comprises the following modules:

- Module 1 Multiway Filter Board.

- Module 2 Power Supply Unit.

- Module 3 Microprocessor Board.

- d. Module 4 Detector Module.

- Module 5 RF Matching Board.

- Module 6 RF Matching Board.

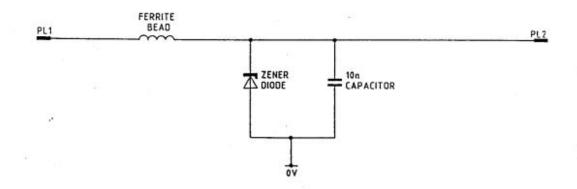

# Module 1 - Multiway Filter Board

Module 1 provides an LC filter and EMP (Electromagnetic Pulse) protection for each of the system control

lines (except EARTH) used by the HF ATU.

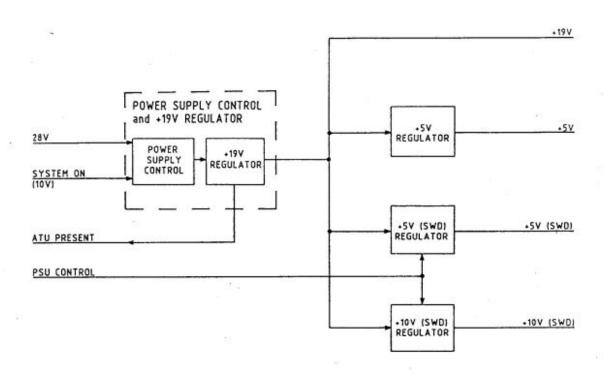

# Module 2 - Power Supply Unit

12. Module 2 provides regulated dc power supplies for Modules 3, 4, 5 and 6 from the unconditioned 28 V vehicle supply. System control signals are routed to/from Module 2 via Module 1.

# Module 3 - Microprocessor Board

- 13. Module 3 contains the Microprocessor, control logic and buffering circuits which decode the various control signals from other equipments and determine the overall operation of the HF R/T. External system controls are fed to/from Module 3 via the equipment's front panel CONTROL connector and Module 1. Control signals to/from Module 3 control the operation of the tuning components on Modules 4, 5 and 6.

- 14. Module 3 is also responsible for distributing regulated dc voltage supplies from Module 2 to Modules 4, 5 and 6.

# Module 4 - Detector Module

15. Module 4 contains detectors which are required by the Microprocessor on Module 3 during the HF ATU's tuning sequence. Module 4 also contains the fine tuning inductors and capacitors, plus their individual selection relays which are controlled by the Microprocessor on Module 3.

# Module 5 - RF Matching Board

16. Module 5 contains the medium tuning inductances and the coarse tuning capacitors plus their individual selection relays. The relays are controlled by the Microprocessor on Module 3.

# Module 6 - RF Matching Board

17. Module 6 contains the coarse tuning inductances and broad band capacitors plus their individual selection relays. The relays are controlled by the Microprocessor on Module 3. The RF power output to the antenna (via the rear panel) is also taken from this module.

FIGURE 3 - HF ATU EQUIPMENT BLOCK DIAGRAM

### **FUNCTIONAL DESCRIPTION**

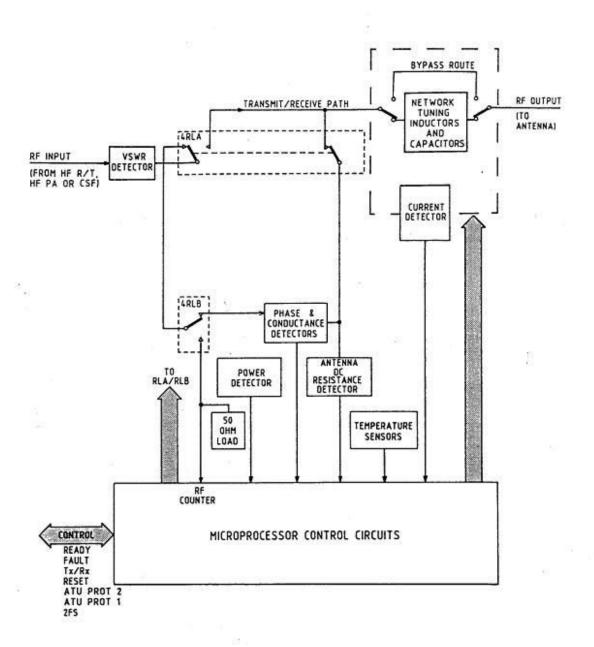

- 18. The HF ATU's tuning sequence (tuning takes approximately 1.5 seconds) and subsequent quiescent operation are determined by the system control signals applied to the front panel CONTROL connector. A functional block diagram of the HF ATU is shown in Figure 4. The major functional elements within the equipment are as follows:

- The detectors which monitor the transmission line.

- b. The Network Tuning Inductors and Capacitors which are selected by the microprocessor to match the nominal 50 Ohm output impedance of the HF R/T, the HF PA or the HF CSF, to the impedance of the antenna.

- The Microprocessor Control Circuits which control all aspects of the HF ATU operation.

- 19. The operation of relay 4RLA determines whether the RF Input is routed to the Network Tuning Inductors and Capacitors, or to the detector circuits. When the equipment is correctly tuned, 4RLA is energised and the transmit/receive path is through the VSWR Detector, 4RLA, the Network Tuning Inductors and Capacitors, to the antenna. With reference to Figure 4, 4RLA is shown in the de-energised state to connect the RF input to the detector circuits via 4RLB. Relay 4RLB, also shown in the de-energised state in Figure 4, determines whether the RF is applied to the Power Detector or the Phase and Conductance Detector. Both relays are controlled by the Microprocessor Control Circuits. 4RLA and 4RLB denote that relays RLA and RLB are housed on Module 4.

# **Tuning Sequence**

- 20. When the HF R/T is initially switched on, or when its operating frequency changes, the HF R/T issues a RESET signal which causes all external units in the output path to prepare for new parameters. On receipt of a RESET signal from the HF R/T, the Microprocessor Control Circuits switch all previously selected tuning components out of circuit (shown as Bypass on Figure 4). With 4RLA energised, this effectively shorts the RF INPUT connector to the antenna. The Microprocessor then sets the system FAULT and READY lines low. READY, connected to the HF R/T via the CONTROL connector, will remain low until the tuning sequence is successfully completed.

- 21. When the next pressel operation sets the HF R/T to transmit, it informs the HF ATU by setting the Tx/Rx control line low. The RF Output from the HF R/T is an unmodulated 5 Watt tuning signal at the HF R/T's transmit frequency. On receipt of the Tx/Rx signal, the Microprocessor Control Circuits de-energise 4RLA (from its energised HF ATU 'tuned' position) and 4RLB is energised. This connects the RF tuning signal to the 50 Ohm Load and the Power Detector. The 50 Ohm Load is used to terminate the RF TUNE signal.

- 22. The output of the Power Detector is applied to the Microprocessor Control Circuits as a dc voltage proportional to the amplitude of the RFTUNE signal. With 4RLA de-energised, the antenna circuit is connected to the Antenna DC Resistance Detector via the Bypass Route in the Network Tuning Inductors and Capacitors.

- 23. If the CW tuning signal is not between 1 and 7 W, or the antenna dc resistance is less than 75 Ohms, the tuning sequence is aborted. When this occurs, the Microprocessor Control Circuits set FAULT high to signal the fault condition to the HF R/T.

- 24. If the tuning signal power and antenna de resistance are within limits, the CW carrier frequency is measured and the resultant value used by the Microprocessor Control Circuits to latch in the initial tuning components. 4RLB is de-energised by the Microprocessor Control Circuits, and the combined impedance of the tuning circuit and the antenna is measured by the Phase and Conductance Detectors. The initial tuning circuit is then amended as required by adding/deleting tuning components. This iterative process of measurement and amendment is repeated until an impedance value of approximately 50 Ohms (20 milli-Siemens conductance) is achieved with the reactance component of the impedance tending towards zero.

FIGURE 4 - HF ATU FUNCTIONAL BLOCK DIAGRAM

- 25. The Microprocessor Control Circuits then measure the VSWR from the VSWR Detector to determine if the tuning process has been successful. If a forward to reverse voltage standing wave ratio of 3:1 (or better) is found, the equipment is correctly tuned. A ratio greater than 3:1 indicates the equipment is not correctly tuned; in this case, the Microprocessor Control Circuits set the FAULT line active high to inform the HFR/T that HFATU tuning has failed.

- 26. When the tuning sequence is successfully completed, the HF ATU informs the HF R/T by setting the READY line active high. 4RLA is then energised by the Microprocessor Control Circuits to connect the RF input through the matched tuned circuit to the antenna.

# 2FS

- 27. In the 2FS mode of operation, the HF R/T receives on one frequency and transmits on another. To conform to this requirement, the transmit and receive signal paths through the HF ATU are different. The transmit path follows the normal operating path through the tuned inductors and capacitors, but on receive all the tuning components are switched out of circuit and the data regarding the component configuration put into memory.

- 28. Because the tuning inductors are 'switched out' by short circuiting, the receive path is a direct connection between the antenna and the RF INPUT connector. When switching from receive to transmit, the tuned circuit component data is retrieved from memory and the components switched back in.

### **Protection Circuits**

- 29. The Microprocessor Control Circuits generate ATU PROT 1 and ATU PROT 2 system control signals to instigate a reduction in the RF input power to the HF ATU. A combination of ATU PROT 1 and ATU PROT 2 logic levels instigating different reductions in input power under the following conditions:

- a. When excessive currents flowing in the network tuning components are detected by the Current Detector.

- b. When excessive temperatures are detected by the Temperature Sensors on the HF ATU chassis.

- c. Poor VSWR (the VSWR Detector is always in circuit when the HF R/T is transmitting).

- d. When a low supply voltage is identified by the Microprocessor Control Circuits.

### MICROPROCESSOR PROGRAM CONTROL

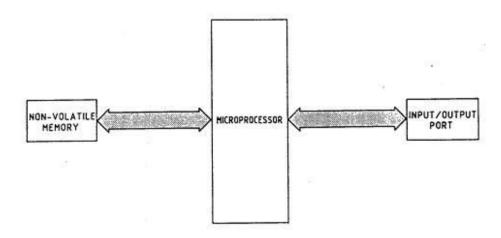

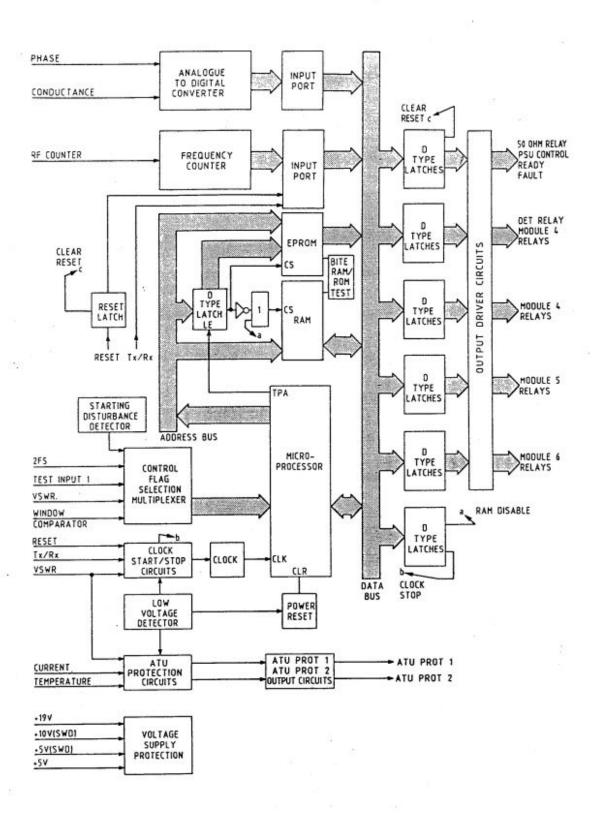

30. The operation of the HF ATU is controlled and monitored by Microprocessor software stored on Module 3. As shown in Figure 5, the Microprocessor system comprises a Microprocessor, a Non-Volatile Memory and a number of Input/Output Ports.

# FIGURE 5 - MICROPROCESSOR SYSTEM BASIC BLOCK DIAGRAM

- 31. The term Non-Volatile Memory means the contents of the memory will not be lost when power to the system is removed. This type of memory is used to provide permanent storage for the sequence of instructions and data that constitute the Microprocessor's program. The HF ATU uses an Erasable Programmable Read Only Memory (EPROM) as the Non-Volatile Memory device, in which the program data is made 'permanent' by applying an overvoltage (about 25 V) to its control gate. Once this gate has been charged, the only method of erasing the data is by exposure to ultraviolet light.

- 32. The Microprocessor is a single integrated circuit which executes the program instructions and reacts to events from external devices. Various registers in the Microprocessor have specific roles and carry out the following actions:

- Hold instructions currently under execution.

- b. Perform logic and arithmetical functions.

- Hold input and output data, addresses and status information.

- 33. Small amounts of volatile Random Access Memory (RAM) are used to hold transient results produced during processing, such as intermediate results produced from arithmetic operations.

- 34. The Input/Output Ports enable the Microprocessor to communicate with external units. A detailed description of the ports is given in the detailed description of Module 3.

- 35. When the Microprocessor is switched on, the start point of the program in memory is addressed by the Microprocessor to fetch its first instruction. The Microprocessor then executes each sequential element of the program, using each instruction to process the program's requirements. Instructions and data in the HF ATU's Microprocessor system are made up of combinations of '1's and '0's to form a byte (8 bits). In physical terms, the program, with instructions of one, two or three bytes, appears as shown in Figure 6; the ones and zeros contain the information which instructs the Microprocessor on what action to take next.

|        | 00110010 | ±                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ADDRESS n |   | man array | ADDRESS 2 |     |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---|-----------|-----------|-----|

|        |          | The state of the s | 1         |   |           | 0         |     |